Parallel computing chips with high versatility and high performance, become a leader

in the filed of parallel computing

Chips based on RPP architecture will better meet the high-performance

computing needs of various scenarios

The core team has more than fifteen years of professional R&D experience in the

field of chip design and development

Parallel computing chips with high versatility and high performance, become a leader

in the filed of parallel computing

Chips based on RPP architecture will better meet the high-performance

computing needs of various scenarios

The core team has more than fifteen years of professional R&D experience in the

field of chip design and development

Parallel computing chips with high versatility and high

performance, become a leader in the filed

of parallel computing

Chips based on RPP architecture will better meet the

high-performance computing needs of various scenarios

The core team has more than fifteen years of

professional R&D experience in the

field of chip design and development

Our team

- Attracting outstanding integrated circuit talent globally, the AzurEngine chip team has an average of 15 years of experience in the industry.

- AzurEngine is led by international teams with outstanding R&D and management experience.

Innovative chip architecture

- RPP is a novel processor architecture for computer vision applications, which combines the general processor’s programmability and ASIC’s power/cost efficiency together. With the unique architecture, the programmer can focus on the algorithm design without paying attention to the HW details.

Our vision

- Fill the gaps in the fast-developing high versatility and high-performance parallel computing chip field, and become a leader in the parallel computing industry.

ABOUT US

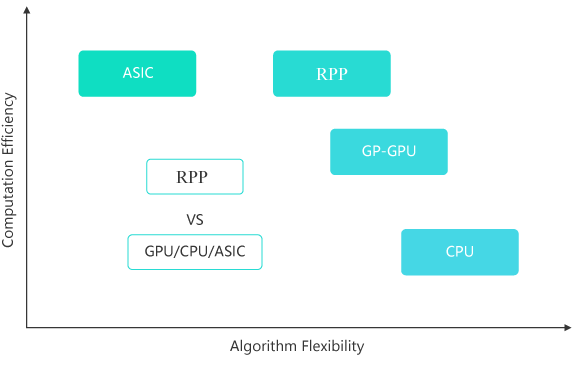

AzurEngine has developed an innovative processor architecture called RPP (Reconfigurable Parallel Processor), which bridges the gap of programmability and power efficiency between GP-GPU and ASIC (TPU/NPU).

RPP is a high-performance, efficient, and compatible chip solution for parallel computing at the edge and in the data center.

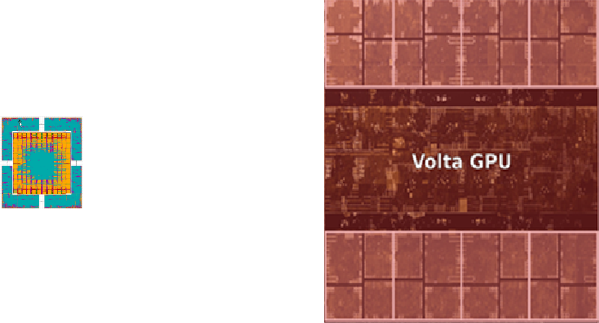

Small and Powerful

Our innovative RPP architecture enables high-efficiency, general-purpose, and low-power GP-GPU chips.

Existing GPU solutions are pushing the limits of Si area and system power consumption, mostly relying on process technology advancements for PPA improvement.

RPP-based chips provide a fully programmable solution with 3x reduction in Si area, improved performance, and lower power consumption.

AzurEngine RPP architecture

1024 RPP computing unit

NVIDIA Volta architecture

1024 GPU computing unit

Balance performance and versatility

Compared with the vector processor architecture, the RPP architecture will provide extremely high computational efficiency. Compared with the current mainstream GP-GPU,

The RPP innovative architecture will bring higher computing density and versatility close to GP-GPU, as well as efficiency comparable to professional chips

Core Products

In recent years, with the rapid development of AI technology, the demand for deep learning-based computer vision applications such as face recognition, car recognition, and logistics inspection has increased rapidly. Faced with the current and future requirements for chip computing power and programming flexibility With rapid growth, the market urgently needs powerful, flexible and low-power parallel computing chips.

GP-GPU chips based on the RPP (Reconfigurable Parallel Processor) architecture can effectively reduce chip costs while taking into account versatility and computing performance, and better meet the market’s long-term demand for chip products.

Application scenario